- 全部

- 默认排序

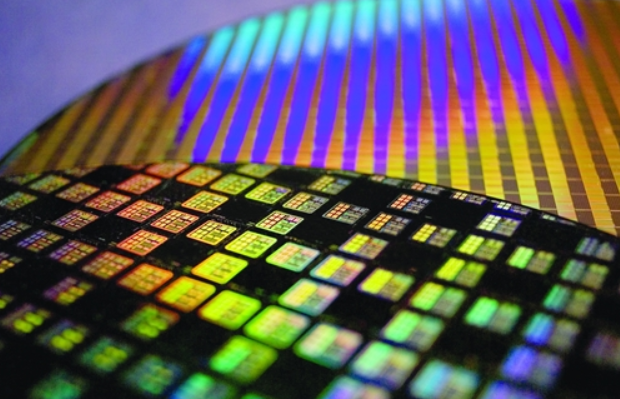

近年来,中国大力发展本土半导体产业,同时也在半导体制造设备领域发力,并且取得了一定的成就,下面我们来看2023年中国半导体设备领域怎么样。据半导体行业组织SEMI发布的最新数据:2023年全球半导体制造设备的销售额达到了1063亿美元,相较

随着信号上升沿时间的减小,信号频率的提高,电子产品的EMI问题,也来越受到电子工程师的重视。高速pcb设计的成功,对EMI的贡献越来越受到重视,几乎60%的EMI问题可以通过高速PCB来控制解决。1高速信号走线屏蔽规则如上图所示:在高速的PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果

EMC整改,真难

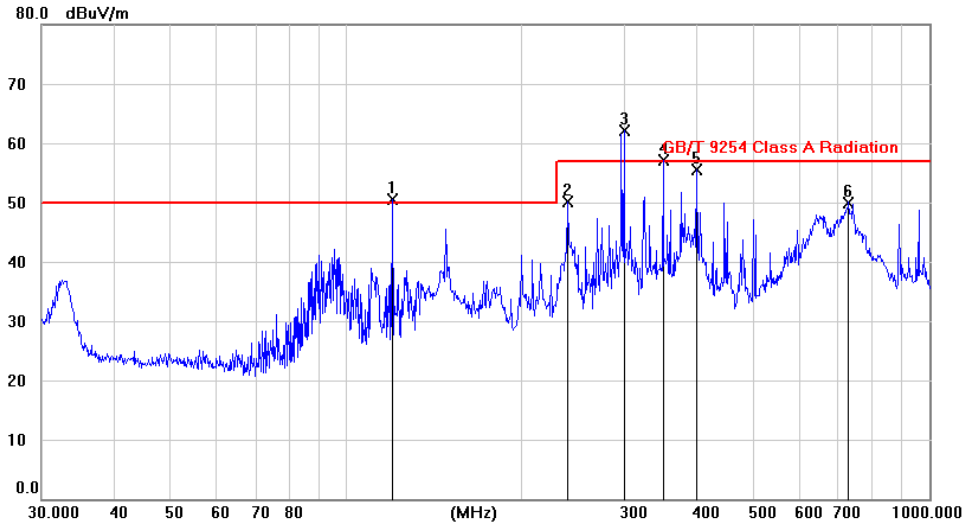

辐射这东西,看不见摸不着,整改还按小时算,一不小心几万块就没了。不得不说,EMC整改,真难。本文主要分享理论 实际案例,文章篇幅较长,建议先收藏再阅读。1. EMI源头是什么?造成EMI问题的辐射源有两类:交变电场(高阻),交变磁场(低阻)。非隔离的DC/DC转换器具有阻抗很低的节点和环路(远低于自

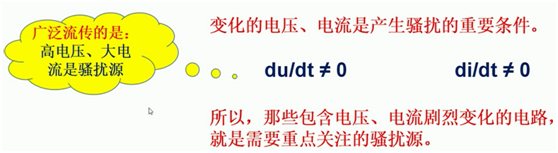

电磁兼容试验中的重要内容就是骚扰发射试验。因此,控制骚扰发射是一项重要的设计内容。为了控制骚扰发射,首先要找到骚扰源,然后采取措施消除它,或者截断它发射骚扰能量的路径。 EMI骚扰源有啥特征呢?以往广泛流传的是:高电压,大电流就是骚扰源。这种说法其实很片面。单纯的一个很高的电压,或者一个很大的电流,

在电子设备的设计和制造过程中,电磁干扰无疑是最为麻烦的问题,为了有效抑制和消除EMI,电子工程师会选择使用一系列专门的整改器件,下面将介绍几种常见的EMI整改器件,希望对小伙伴们有所帮助。1、电容通过充放电特性,电容可灵活抑制不同频率的干扰

在PCB设计中,死铜即孤岛铜算是常见的问题,是指那些没有电气连接,孤立存在电路板上的铜区域,然而很多电子工程师遇见死铜,都在忧虑是否要去除,下面本文将从多角度来分析,希望对小伙伴们有所帮助。1、死铜能带来什么问题?①EMI问题:死铜在电路板

Stratix® 10 FPGA概述Stratix® 10 FPGA和SoC FPGA大幅提高了性能、功效、密度和系统集成度。Stratix 10采用创新Hyperflex FPGA架构,将嵌入式多芯片互连桥接器 (EMIB)、高级接口总线

随着电子产品向高频、高速、高集成度方向发展,电磁干扰(EMI)问题日益凸显,为确保产品质量,提升市场竞争力,降低EMI差异、提高测试精准度成为业界共同关注的焦点,本文将从多方面探讨可行性,希望对小伙伴们有所帮助。1、优化测试环境首先,要想降

MOS管全称为金属氧化物半导体场效应管(Metal Oxide Semiconductor Field Effect Transistor),也被称为MOSFET(Metal-Oxide-Semiconductor Field-Effect

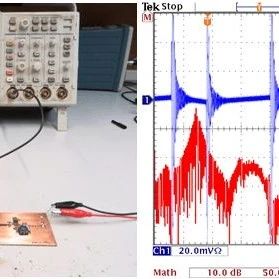

最近想起来,以前在做EMI整改的时候,出现过低频辐射超标,类似下面这种。一般这种问题,我们都会说是时钟线引起的问题。我之前做的产品是摄像头,时钟线加十几根数据线。有一次处理完时钟线后还是超标,因为正好数据线上都串有电阻,我就将电阻都改成了磁珠,想消除因为数据线引起的辐射,改完之后发现还是超标,看不到

扫码关注

扫码关注